RISC-V

RISC-V is an ISA specification but not a processor.

The RISC-V ISA is defined as a base integer ISA, which must be present in any implementation, plus optional extensions to the base ISA. The base is carefully restricted to a minimal set of instructions sufficient to provide a reasonable target for compilers, assemblers, linkers, and operating systems.

Each base integer instruction set is characterized by

- the width of the integer registers

- the corresponding size of the user address space.

There are two primary base integer variants, RV32I and RV64I. The suffix “I” means the base integer ISA. Diffenrent standard extensions add different suffixes.

The base RISC-V ISA has a little-endian memory system, but non-standard variants can provide a big-endian or bi-endian memory system.

Table of contents

Reference:

- The RISC-V Instruction Set Manual Volume I: User-Level ISA

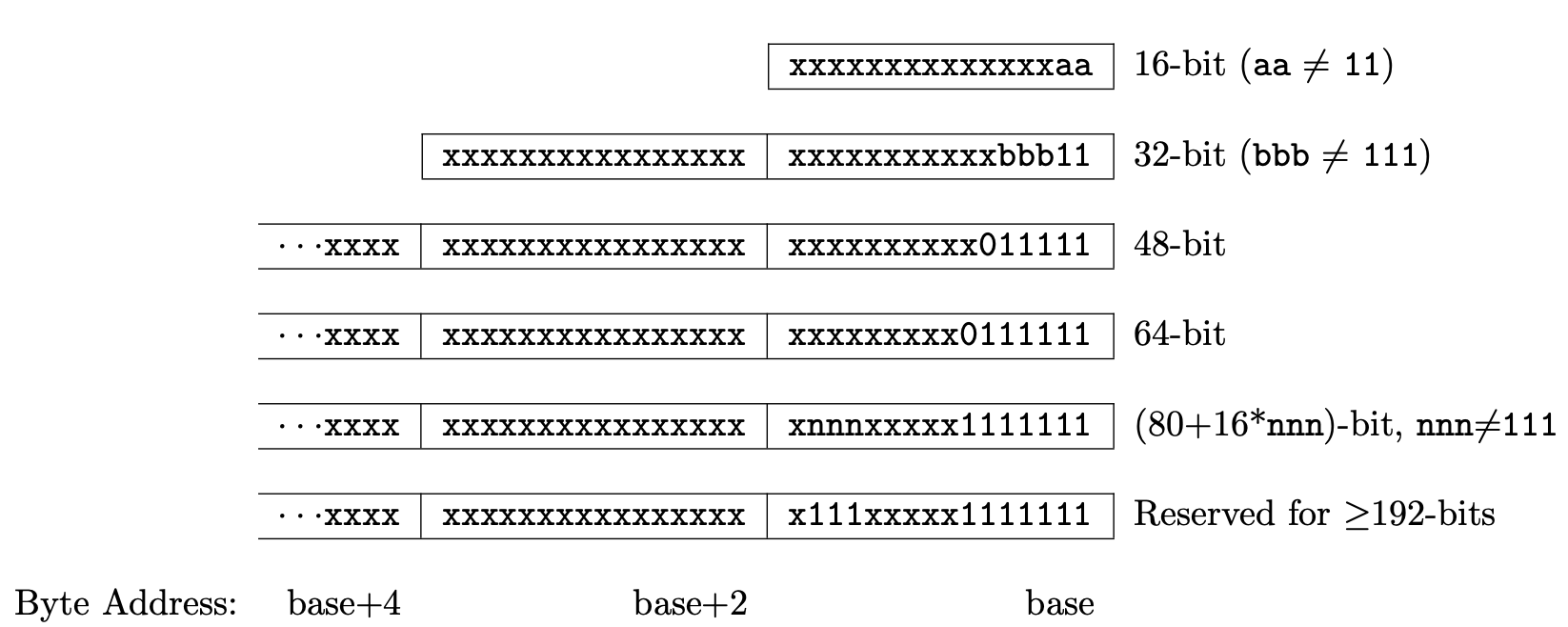

Instruction-Length Encoding

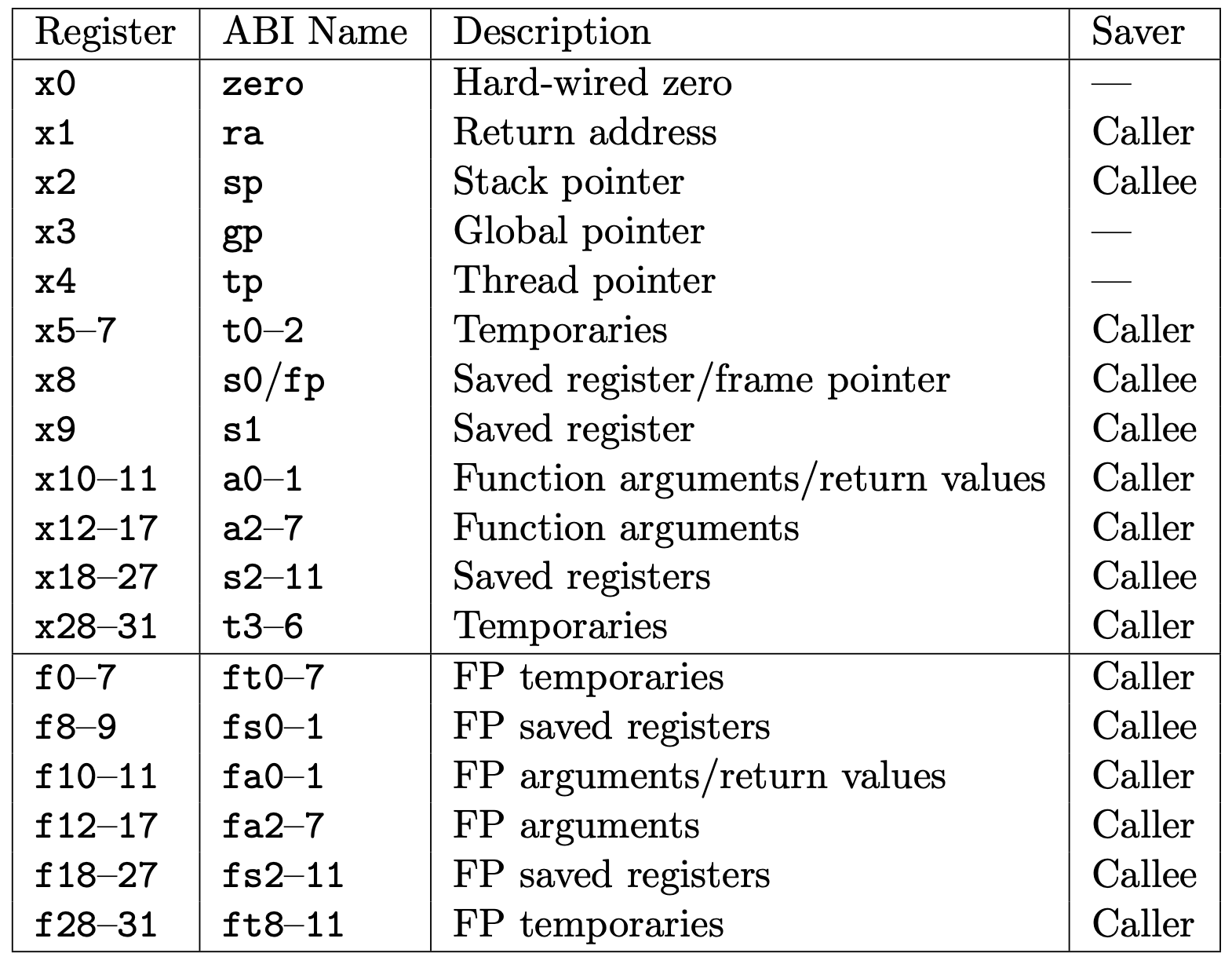

Register

At user-level, there are 32 general registers (named x0/zeor, x1, …, x31) plus a ip register.

The gp (Global Pointer) register is a solution to further optimise memory accesses within a single 4KB region. The gp register should be loaded during startup with the address of the __global_pointer$ symbol and should not be changed later. This process is also called relaxing, and can be disabled by -Wl,--no-relax.

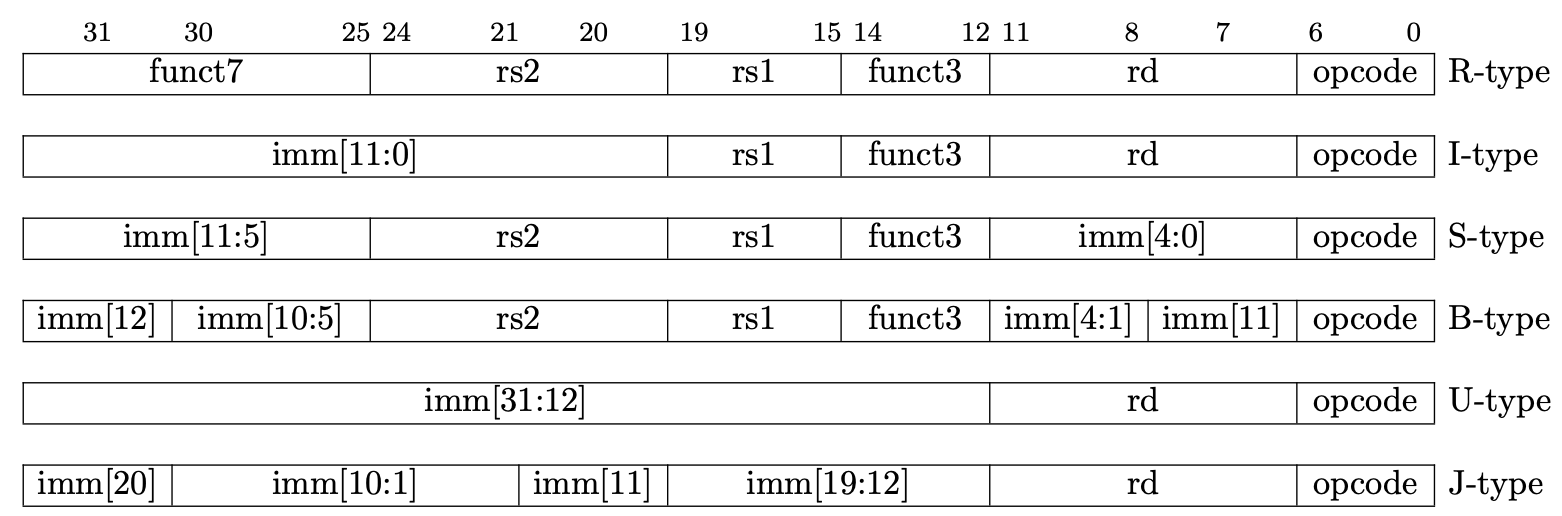

Instruction Formats